Questasim 10 Crack Load

I am new to using UVM in modelsim 10.4b. I am trying to check if my class is getting compiled, but I am getting the following compilation error. Also, if anyone can point me to the UVM exection flow, that would be really helpful. I have searched on the online resources.

Amar chitra katha stories. List of Amar Chitra Katha Issues #1 to #10. Amar Chitra Katha issues ranging from #1 to #10 were reproductions of western fairy tales.They were never published in English but were published in Kannada first and then the following Indian languages-Hindi, Marathi, Gujarati, Bengali, Tamil, Telugu, Malayalam. EMBED (for wordpress.com hosted blogs and archive.org item tags). Anant Pai popularly known as Uncle Pai, was an Indian educationalist and creator of Indian comics, in particular the Amar Chitra Katha series in 1967, along with the India Book House publishers, and which retold traditional Indian folk tales, mythological stories, and biographies of historical characters. Amar Chitra Katha. Amar Chitra Katha offers a variety of illustrative and engaging stories for kids. Our online bookstore has a collection of moral stories that teach valuable lessons to children. Our online library has bedtime story books too.

Class fifo_trans_item extends uvm_sequence_item; rand bit [15:0] data_in; rand bit push; rand bit pop; rand bit w_en; rand bit r_en; endclass This is the error I am getting.If this is a tool related issue, please redirect me to the forum for asking this question. Loading project MIPS # reading modelsim.ini # Loading project UVM_tb # UVM Details: design does not contain any UVM components, UVM debugging is disabled, or an unknown questa_uvm_pkg has been loaded. # Compile of sequence.sv failed with 2 errors.

Jan 1, 2018 - Questasim 10 Crack Load. Advanced Code Coverage ModelSim's advanced code coverage capabilities and ease of use lower the barriers for.

** Error: (vlog-13069) /afs/asu.edu/users/s/m/u/smukerji/sequence.sv(1): near 'uvm_sequence_item': syntax error, unexpected IDENTIFIER. ** Error: /afs/asu.edu/users/s/m/u/smukerji/sequence.sv(1): Error in class extension specification.

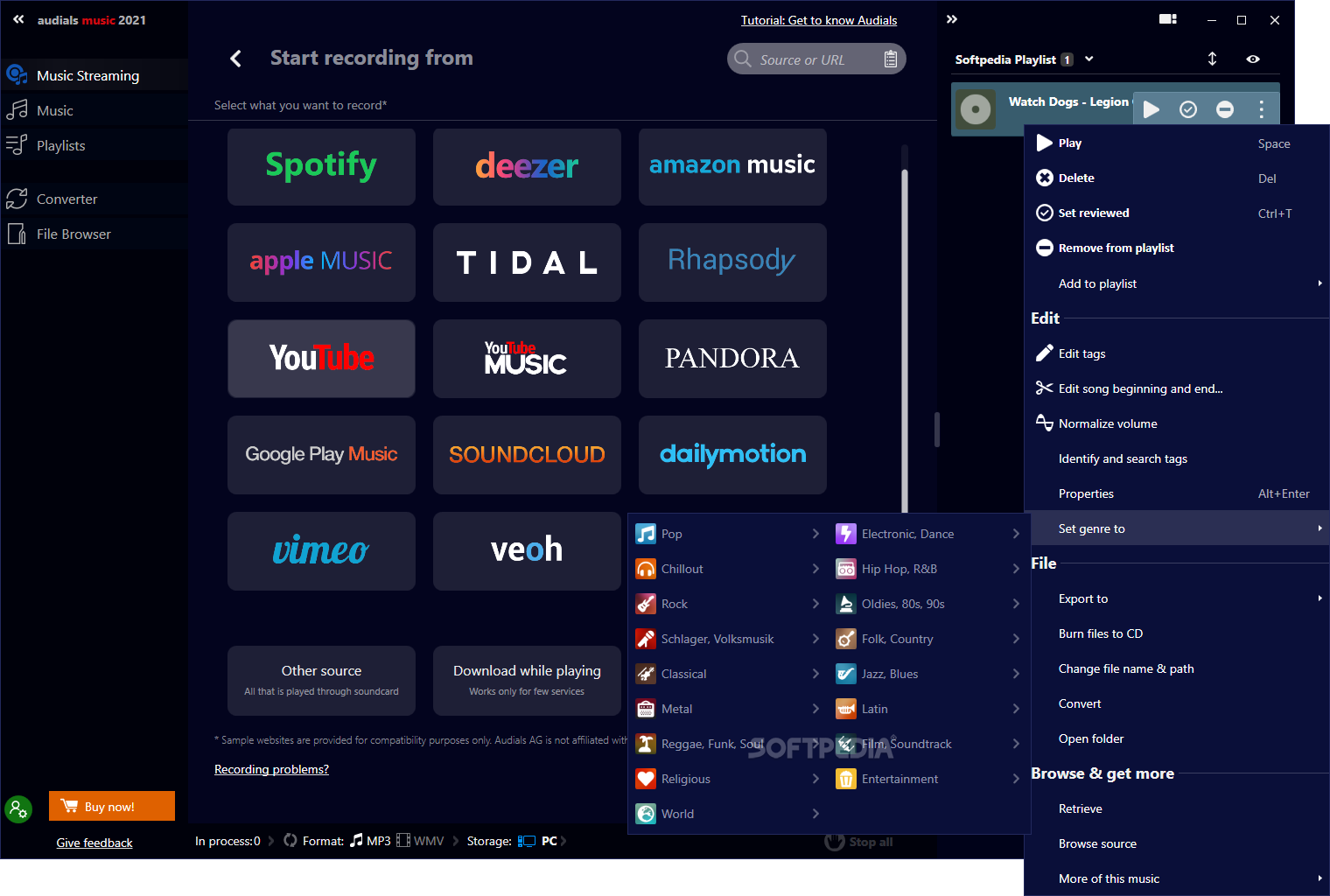

Bose sounddock serial number lookup. Mentor.Graphics.QuestaSim.v10.4c Questa’s core simulation and debug engine The Questa® Advanced Simulator combines high performance and capacity simulation with unified advanced debug capabilities for the most complete native support of Verilog, SystemVerilog, VHDL, SystemC, PSL and UPF. The Questa Advanced Simulator is the core simulation and debug engine of the Questa Verification Platform; the comprehensive advanced verification platform capable of reducing the risk of validating complex FPGA and SoC designs. Advanced Debug with Questa ON-DEMAND WEB SEMINAR Questa spans the levels of abstraction required for complex SoC and FPGA design and verification from TLM (Transaction Level Modeling) through RTL, gates, and transistors and has superior support of multiple verification methodologies including Assertion Based Verification (ABV), the Open Verification Methodology (OVM) and the Universal Verification Methodology (UVM) to increase testbench productivity, automation and reusability. FEATURES High Performance and Capacity Assertion Based Verification Test Automation Questa Verification Management Integrated Multi-Language Debugging Power Aware Verification High Performance and Capacity The Questa Advanced Simulator achieves industry-leading performance and capacity through very aggressive, global compile and simulation optimization algorithms of SystemVerilog and VHDL, improving SystemVerilog and mixed VHDL/SystemVerilog RTL simulation performance by up to 10X. Questa also supports very fast time-to-next simulation and effective library management while maintaining high performance with unique capabilities to pre-optimize and define debug visibility on a block by block basis enabling dramatic regression throughput improvements of up to 3X when running a large suite of tests.

To increase simulation performance for large designs with long simulation times, Questa also has a Multi-Core option. Questa Multi-Core takes advantage of modern compute systems by partitioning the design to run in parallel on multiple CPU’s or computers using either automatic or manually driven partitions. To achieve even greater performance, Questa supports TBX; the highest performance Transaction Level link to the Veloce platform enabling a 100x increase in performance with debug visibility and a common testbench.